# DUROC Demonstrator in Rad-Hard N7 Technology

April 2<sup>nd</sup> 2025

#### Alp KILIC

#### RISC-V IN SPACE

This project has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement N°101004206

# **Context in 2025 and Beyond**

#### COMPONENTS FOR SPACE CHALLENGES

SOVEREIGNTY

0

cnes

COMPETITIVENESS

FOR THE BENEFIT OF ECOSYSTEM

SPACE SPECIFICITIES

Source: Florence MALOU - ESCCON 2025

### Courtesy of CNES (French National Space Agency)

© 2025 Nanoxplore SAS Company

RÉPUBLIQUE FRANÇAISE

## **Questions for all of us**

| Sovereignty         | <ul> <li>Could Open Source be an answer to geopolitical instabilities?</li> </ul> |  |  |

|---------------------|-----------------------------------------------------------------------------------|--|--|

| Competitiveness     | <ul> <li>How to get rid of the technical dept and move forward?</li> </ul>        |  |  |

| Ecosystem           | <ul> <li>How can we stop reinventing the wheel?</li> </ul>                        |  |  |

| Space Specificities | <ul> <li>Are we ready for new challenges?</li> </ul>                              |  |  |

### Who Are We?

**Solution** French Based Company : Paris, Montpellier, Grenoble

**140+ Employees with more than 90% R&D Engineers**

**Offer products for Hi-Rel markets**

#### **3** different products offering:

- High reliable SoC FPGA

- ASIC design services

- Silicon IPs

**⊘** ITAR Free Technology

**Solution Space & Defense markets**

### What we do?

|                                                                                     | oprocessor Sub                                                                      | system                                                                                  |                                                  |                                             |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------|

|                                                                                     | Debug & Trace                                                                       |                                                                                         |                                                  |                                             |

| SoC Services                                                                        | Pro                                                                                 | cessing Unit                                                                            | External Memor                                   | y Connectivity                              |

| Multichannel DMA<br>V&T Monitor<br>Clock & Reset<br>Error Manager<br>Boot SpaceWire | ARM <sup>®</sup><br>Cortex <sup>™</sup> -R52<br>ECC NEON™<br>MPU FPU<br>GIC<br>Core | ARM <sup>®</sup><br>Cortex <sup>™</sup> -R52<br>ECC NEON <sup>™</sup><br>MPU FPU<br>GIC | DDR2/3/4 w/ RS<br>FLASH<br>On-chip Memor<br>eRAM | y SPI<br>SpaceWire<br>JTAG<br>UART<br>GPIOs |

| FPGA Fa                                                                             | abric                                                                               | High Speed Connec                                                                       | ctivity                                          | General Connectivity                        |

| DSPs <ul> <li>19x24 Mult.</li> <li>Preadder</li> </ul>                              | DPRAMs <ul> <li>True Dual Port</li> <li>48 Kb</li> <li>36 Kb w/EDAC</li> </ul>      |                                                                                         | Iex I/O<br>to 1.8V<br>PHY<br>2/3/4 PHY           | <b>GPIO</b> • 1.8V to 3.3V                  |

#### • NG-ULTRA

- Dual SoC component :

- Quad Cortex-R52

- 500K LUTs FPGA Fabric

- 28nm FDSOI Process

- SEE Immune

- Sovereign supply chain

- First flight models already delivered

- ... and other SoC FPGAs & FPGAs with flight heritage

# Project – H2020

### Design and validation of Ultra-Reprogrammable sOCs

- Specify and design the next generation of ultrareprogrammable SoC (ULTRA 7) taking benefit of lesson learnt from DAHLIA project

- Validate the SoC on a rad-hard demonstrator in 7nm FinFET technology from TSMC

- Validate reliability and radiation hardening performance of 7nm FinFET

- Introduce SiP concept for space application

This project has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement N°101004206

## **Project Partners**

### Design and validation of Ultra-Reprogrammable sOCs

# RISC-V Focus

### Design and validation of Ultra-Reprogrammable sOCs

- Specify and design the next generation of ultrareprogrammable SoC (ULTRA 7) taking benefit of lesson learnt from DAHLIA project

- Validate the SoC on a rad-hard demonstrator in 7nm FinFET technology from TSMC

- Validate reliability and radiation hardening performance of 7nm FinFET

- Introduce SiP concept for space application

This project has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement N°101004206

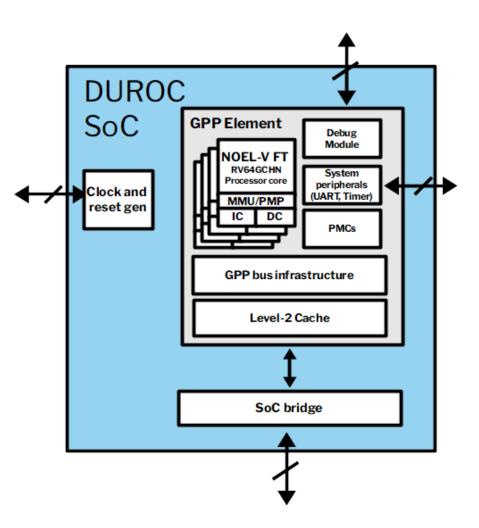

# **Demonstrator in N7**

- Based on Frontgrade Gaisler General Purpose (GPP) element

- Four 64-bit dual-issue NOEL-V FT RISC-V core

- Private level-1 cache

- Shared level-2 cache

- Radiation Constraints

- TID test up to 150krad

- Single Event Latchup (SEL): Target LET > 80 MeV.cm<sup>2</sup>/mg.

- Single Event Upset (SEU) for FF : target LET > 62 MeV.cm<sup>2</sup>/mg.

- Single Event Functional Interrupt (SEFI): target LET > 62 MeV.cm<sup>2</sup>/mg.

- Thermal Constraints

- Operational Temperature Range: -40°C to +125°C.

- Samples in Q4 2025

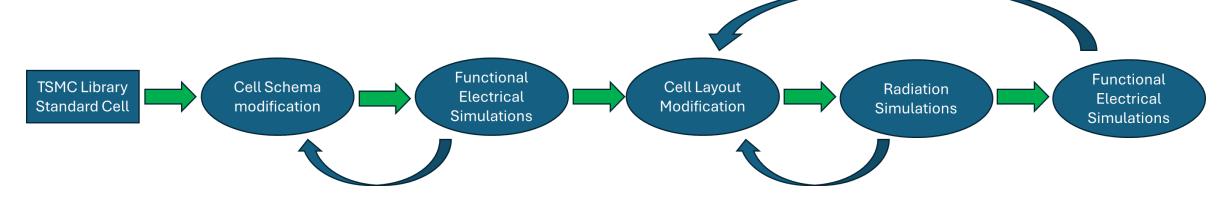

# Rad-Hard Standard Cell Development (1)

#### **Standard Cell Radiation Hardening flow**

- TSMC foundation standard cells

- 3 different "flavors" : SLVT, LVT and SVT

- 2 different families: High Density (HD) and High Speed (HS)

- NX's first hardening target:

- LVT (good power vs. performance trade-off)

- Development with both HD and HS

- Success criteria: Radiation performance as best as we can (target immunity)

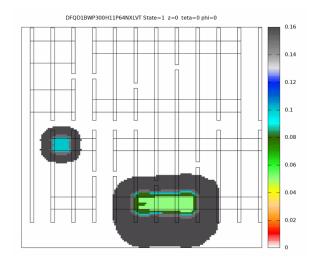

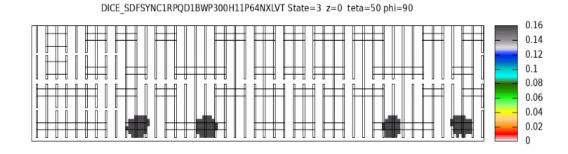

# Rad-Hard Standard Cell Performance (1)

- Standard and Scan DICE based D-Flop

- 300l11p64 configuration (300nm row height / Gate length 11nm / Poly pitch 64nm)

- Radiation performance verification with TFIT.

High-Speed TSMC D Flip-Flop

**High-Speed NX DICE D Flip-Flop**

• DICE DFF vs standard DFF area ratio: 3 – 4 (small silicon contribution)

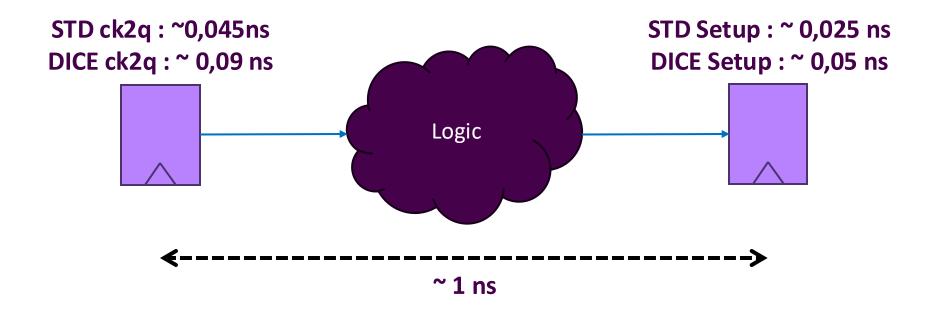

**Critical Path Example :**

### **Radiation hardening overhead in a critical path: ~ 6%**

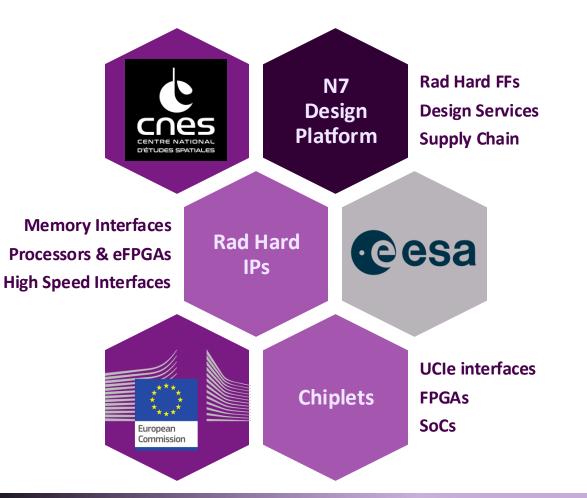

#### For the benefit of Ecosystem: European Space-Ready N7 Design Platform

# Thank You

akilic@nanoxplore.com

#### RISC-V IN SPACE

This project has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement N°101004206

0