# Ensuring Ultra-reliable RISC-V Designs for Space RISC-V in Space Workshop April 2025

## Adnan Hamid, CTO, Breker

### **RISC-V** in Space Verification Requirements

- Verifying any RISC-V core or SoC is complex.

Ensuring coverage for RISC-V space applications greatly compounds this issue

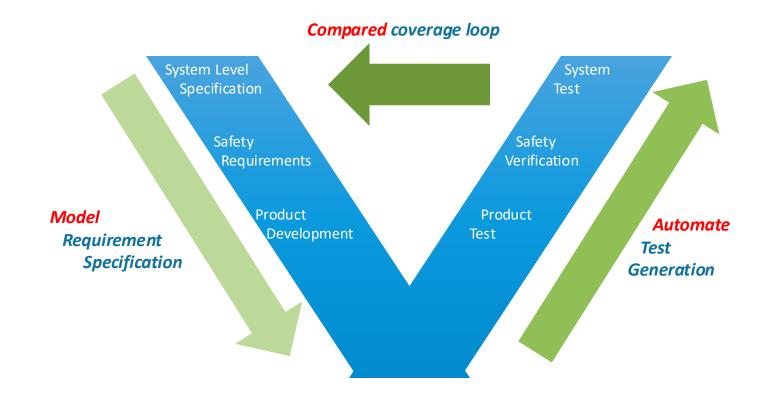

- DO-254 for space applications leverages the V model to drive reliability by linking requirements, test plans, and coverage

- Breker delivers advanced RISC-V test suites to many companies in this space.

We automate V model execution to link requirements to coverage testing

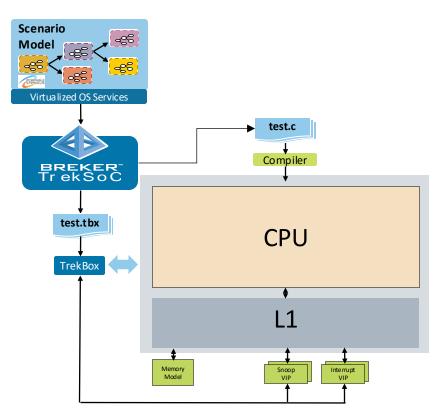

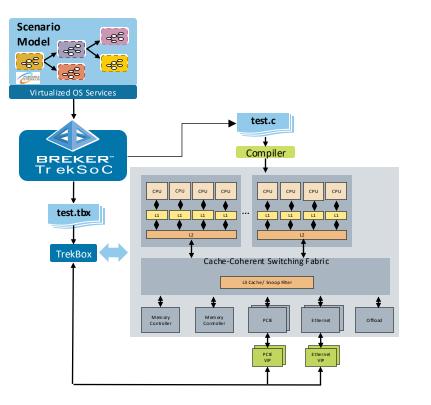

### **Breker: RISC-V Verification Synthesized SystemVIPs**

#### **RISC-V Core Test Functionality**

| Random Instructions       | Do instructions yield correct results              |

|---------------------------|----------------------------------------------------|

| Register/Register Hazards | Pipeline perturbations dues to register conflicts  |

| Load/Store Integrity      | Memory conflict patterns                           |

| Conditionals and Branches | Pipeline perturbations from synchronous PC change  |

| Exceptions                | Jumping to and returning from ISR                  |

| Asynchronous Interrupts   | Pipeline perturbations from asynchronous PC change |

| Privilege Level Switching | Context switching                                  |

| Core Security             | Register and Memory protection by privilege level  |

| Core Paging/MMU           | Memory virtualization and TLB operation            |

| Sleep/Wakeup              | State retention across WFI                         |

| Voltage/Freq Scaling      | Operation at different clock ratios                |

| Core Coherency            | Caches, evictions and snoops                       |

#### **RISC-V SoC Test Functionality**

| Random Memory Tests   | Test Cores/Fabrics/Memory controllers across DDR,<br>OCRAM, FLASH, etc. |

|-----------------------|-------------------------------------------------------------------------|

| Random Register Tests | Read/write test to all uncore registers                                 |

| System Interrupts     | Randomized interrupts through CLINT                                     |

| Multi-core Execution  | Concurrent operations on fabric and memory                              |

| Memory Ordering       | For weakly order memory protocols                                       |

| Atomic Operation      | Across all memory types                                                 |

| System Coherency      | Cover all cache transitions, evictions, snoops                          |

| System Paging/IOMMU   | System memory virtualization                                            |

| System Security       | Register and Memory protection across system                            |

| Power Management      | System wide sleep/wakeup and voltage/freq scaling                       |

| Packet Generation     | Generating networking packets for I/O testing                           |

| Interface Testing     | Analyzing coherent interfaces including CXL & UCIe                      |

| SoC Profiling         | Layering concurrent tests to check operation under stress               |

| Firmware-First        | Executing SW on block or sub-system without processor                   |

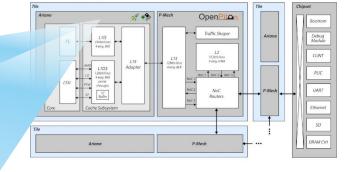

### Applying the tests to single or multi-HART SoCs

Testbench control needed for

- External Interrupts,

- IOMMU,

- Debug Extension

Multi-core tests needed for

- AMO/atomics

- CMO/cache flush, invalidate

- RVWMO Memory Ordering

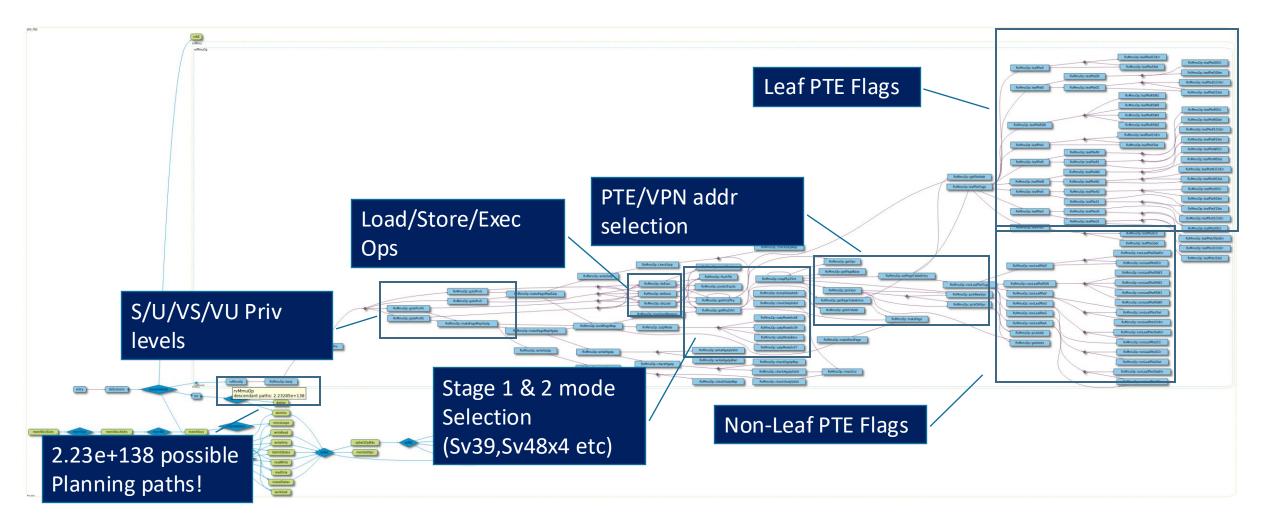

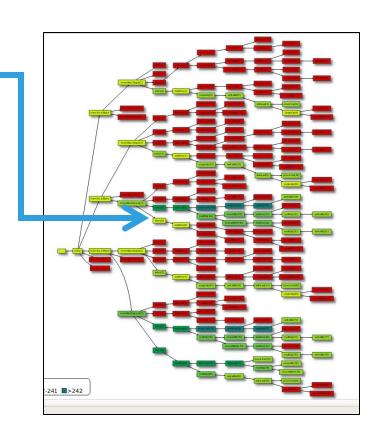

#### Example Scenario Graph: RISC-V MMU Hypervisor Executable Test Plan

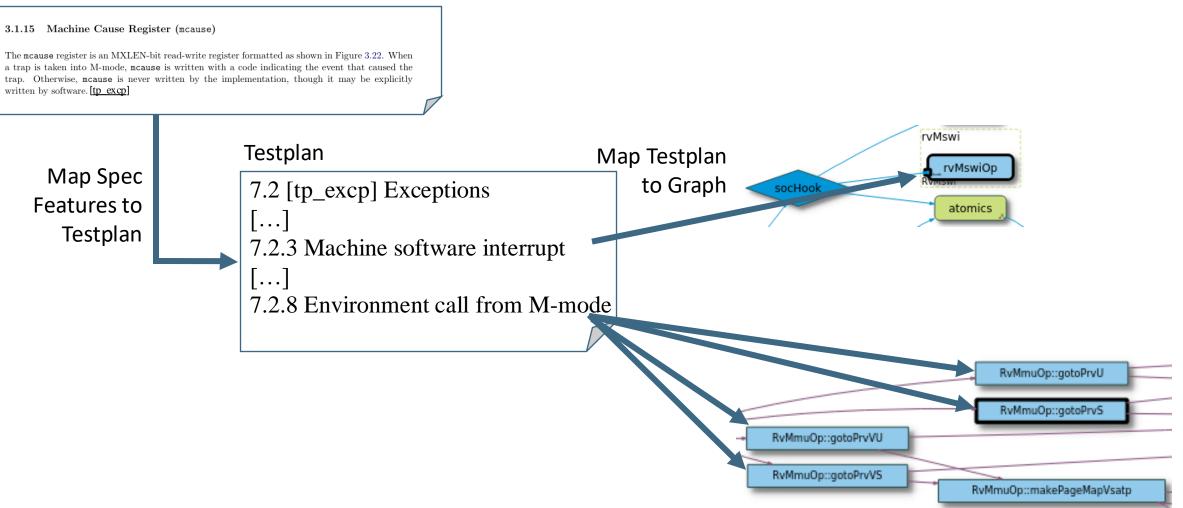

### Automating the DO-254 V-Model

#### Ensuring the rigorous verification of device requirements

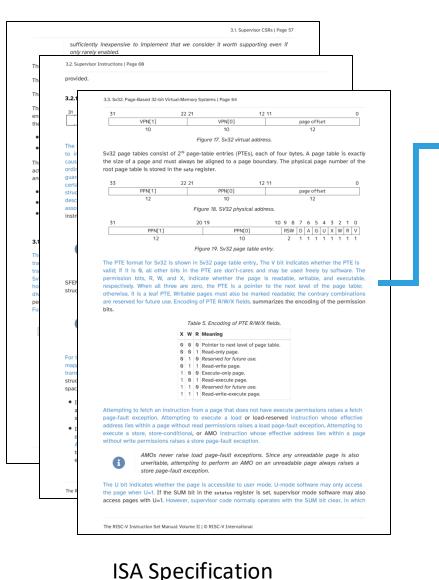

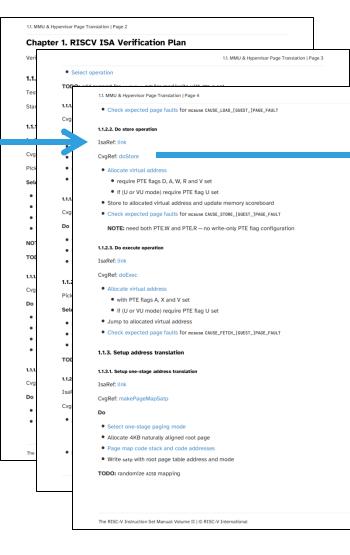

#### Use Appropriate ISA Specs, Derive Test Plan, and Drive Coverage

**RISCV** Test Plan

#### **Coverage Reports**

BREKER

### **Traceability for DO-254 Systematic Testing**

#### Specification

### **Breker RISC-V in Space Summary**

- Meeting RISC-V space applications verification needs requires advanced techniques

- Automating the DO-254 V model allows the linkage of requirements with tests and coverage

- Breker delivers this level of automation using test suite synthesis and RISC-V SystemVIP

Miguel Koch Breker European Director

He is at the conference For more information, feel free to ask him

## Thanks for Listening! Any Questions?